### Accelerate Cloud Computing with MapReduce Accelerator

Christoforos Kachris, Ph.D. Senior Research Engineer Democritus University of Thrace, Greece

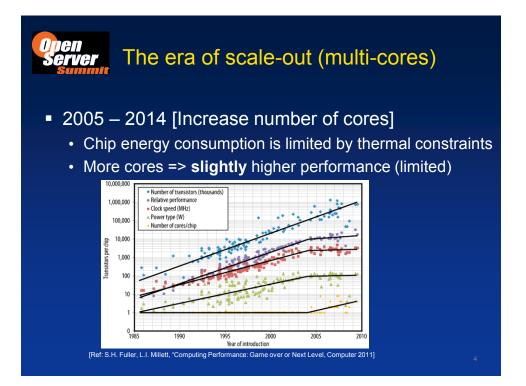

#### The era of Dark Silicon

- Keep increasing core counts can't directly translate into performance improvement (interconnects overhead, off-chip bandwidth, power constraints)

- Dark Silicon: We can put more cores in the same die but due to power constraints we cannot afford to power the whole chip

- Solution: Use abundant die area by utilizing application-specific cores/accelerators

- Dynamically power up only the specific modules designed for the given workload

Santa Clara, CA USA November 2014 [Ref: H. Esmaeilzadeh et al., Dark Silicon and the End of Multicore Scaling, ISCA 2011, N. Hardavellas et al., Toward Dark Silicon in Servers, Micro 2011, M. Ferdman et al., "A Case for Specialized Processors for Scale-out Workloads, Micro, May/June 2014, B. Falsafi, Big Data and Dark Silicon, HiPEAC CSW Athens, 2014]

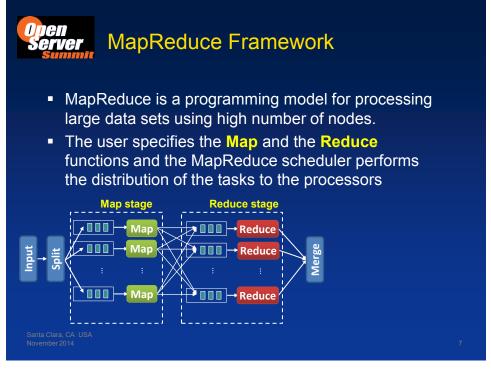

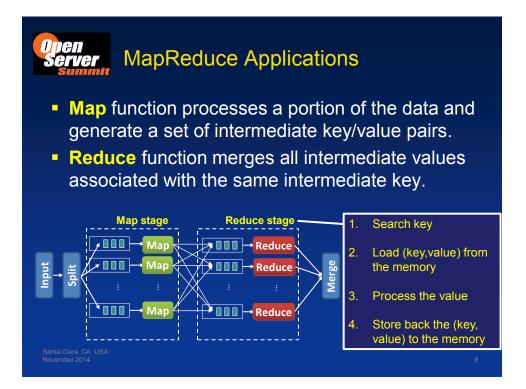

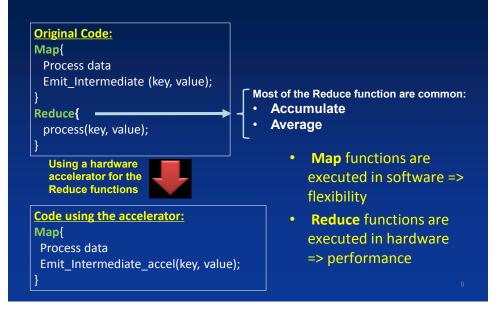

# MapReduce Programming model

**Open** Server

## ARM meets FPGAs: Xilinx Zynq SoC

Oner

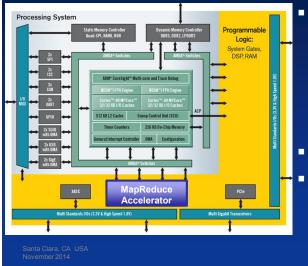

- Performance evaluation in hardware using an Zynq SoC (FPGA with 2 ARM Cortex A9 cores)

- Under Linux

- Phoenix MapReduce benchmark

# Performance evaluation

open Server

Speedup MapReduce Coprocessor Improved Small Large performance (up to 2,5 2.3x speedup) Lower energy Speedup 1,5 consumption 0,5 Alleviate the processor for more WordCount LinearRegr Histogram Kmeans Map tasks Applications Performance evaluation of the Phoenix MapReduce in the Zedboard with Zyng7000 Ref: C. Kachris et al. "A Configurable MapReduce Accelerator for Multi-core FPGAs", FPGA 2014 C. Kachris et al., "A Reconfigurable MapReduce Accelerator for multi-core all-programmable SoCs", SOC 2014

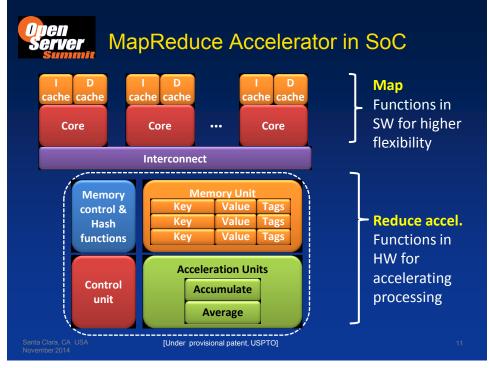

$\Pi$ Utilization of MapReduce accelerator Fine grain (in the SoC) Coarse grain (in the As co-processor in rack) As a stand-alone blade multi-core Server Processors accelerator in the Rack e ||||| e ||||| e ||||| e IIII e ||||| Similar to an encryption e |||||| engine or TCP/IP offload engine

#### **Open** Server **Benefits and Opportunities**

- Applications specific accelerators can be incorporated to future multi-core servers/microservers Chips or Blades to sustain future server's workload

- Need for Open Interface for accelerators

The research project is implemented within the framework of the Action «Supporting Postdoctoral Researchers» of the Operational Program "Education and Lifetong Learning" (Action's Beneficiary: General Secretariat for Research and Technology), and is co-financed by the European Social Fund (ESF) and the Greek State.